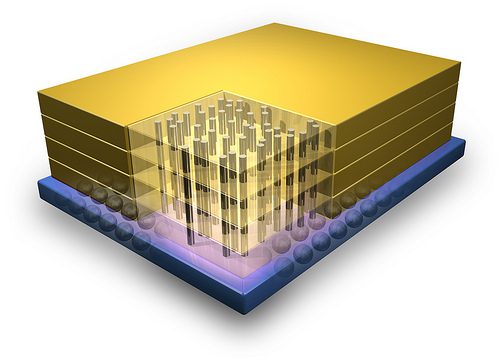

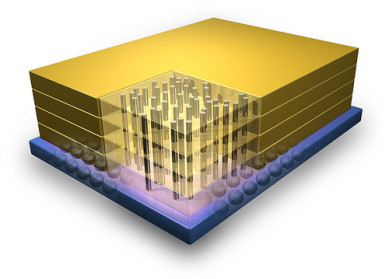

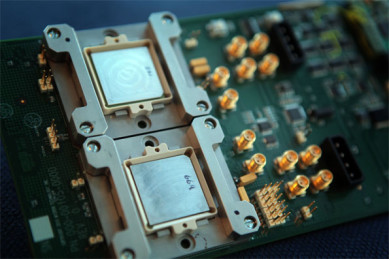

The Hybrid Memory Cube Consortium has been working for 17 months on a global standard that will greatly improve computing memory. The finished specification provides an advanced short-reach (SR) and ultra short-reach (USR) interconnection across physical layers (PHYs) for applications requiring close-proximity memory support for FPGAs, ASICs and ASSPs, such as high performance networking.

A memory cube with 8 links can reach a peak aggregate bandwidth of 320 GB/s. This speed is 20 times that of the DDR3 memory that is currently in use. The HMC Specification 1.0 allows companies to build memory using HMC’s stacked and power efficient technology with 2GB, 4GB, and 8GB chips. HMC 1.0 products are expected to begin appearing in the market by the 2nd half of this year.

The Consortium has also begun work on a new blueprint that will be due in Q1 2014. The new specification will double the individual data link speeds to 28Gbps.